La verità è che non siamo mai soddisfatti. Potremmo fermarci alla versione che "funziona in ufficio", ma chi lavora davvero nel settore IoT sa che il laboratorio è un'illusione. La nostra centralina Sentinel è nata con un'ossessione precisa: non deve solo eseguire codice, deve sopravvivere all'inferno elettromagnetico di un impianto industriale reale.

Innovare, per noi, non significa aggiungere icone colorate su una dashboard, ma passare le notti a capire perché un bus I2C decide di morire quando un motore trifase entra in coppia. Abbiamo torturato i prototipi della Sentinel, spingendoli oltre ogni limite ragionevole, perché preferiamo che il sistema fallisca sulla nostra scrivania piuttosto che nell'impianto di un cliente.

Quello che segue non è un post di marketing per vendervi quanto siamo bravi, ma il diario di bordo di un crash test brutale. Abbiamo tolto ogni protezione, abbiamo rimosso l'isolamento e abbiamo guardato cosa succede quando la teoria si scontra con la realtà dei transienti elettrici.

Stress Test I2C: ESP32 vs Motore Trifase

Nessuna teoria, solo dati dal campo. Abbiamo sottoposto la nuova revisione della centralina a uno stress test elettromagnetico per validare la robustezza del bus I2C in ambiente ostile.

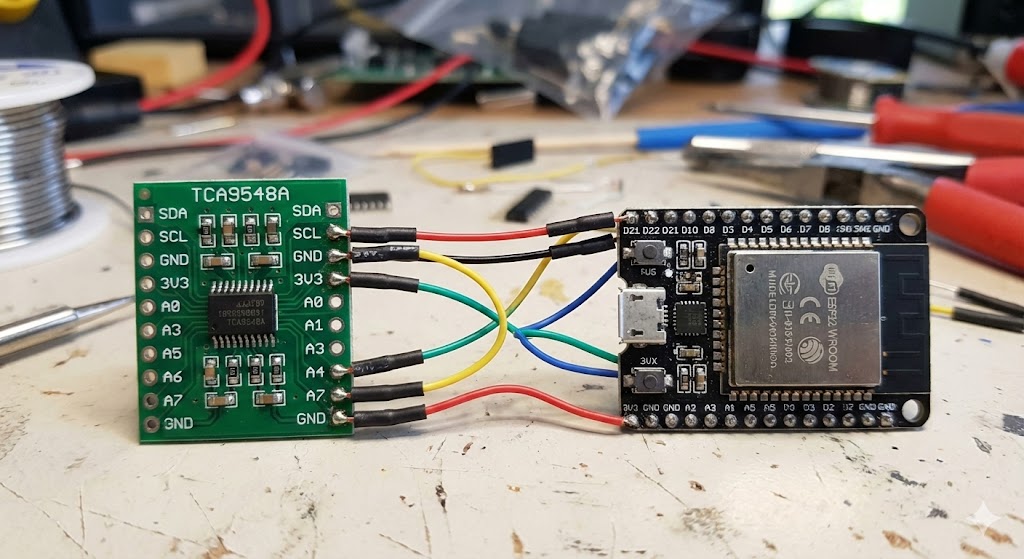

Il setup è minimale e critico: un ESP32 WROOM collegato a un multiplexer TCA9548A tramite cavi jumper standard (non schermati), posizionati a 1 metro da un motore trifase in funzione.

L'obiettivo era dimostrare empiricamente perché l'isolamento galvanico non è un "optional", ma un requisito strutturale. Il confronto tra il segnale in ambiente pulito e quello sotto carico induttivo evidenzia il collasso dell'integrità del segnale.

ANALISI TECNICA SEGNALE I2C

Segnale logico 0-3.3V pulito. Notare la leggera curvatura esponenziale sui fronti di salita (tipica dei resistori di pull-up I2C) e i fronti di discesa netti (pilotaggio open-drain). I livelli logici sono stabili, garantendo la corretta interpretazione dei bit (ACK/NACK, Data).

Fig 1.0: Analisi comparativa dei transienti e del rumore di commutazione sul bus SDA.

- Ground Bounce/VCC Sag: L'onda quadra di base è deformata da fluttuazioni a bassa frequenza (ripple) indotte dai loop di massa non isolati.

- EMI Switching Noise: Il rumore ad alta frequenza (hash) si sovrappone ai livelli logici, rischiando di farli uscire dalle soglie di isteresi (es. un '0' letto come '1').

- Transienti Induttivi (Spikes):

Picchi di tensione violenti (fino a >5V o <0V) causati dalle commutazioni. Effetti:

- Corruzione pacchetto dati (CRC error).

- Latch-up TCA9548A o GPIO ESP32.

- Danno fisico ai pin (assenza diodi clamp).

Senza optoisolatori o buffer I2C dedicati (es. PCA9617A) e con un cablaggio non schermato vicino a carichi induttivi, la comunicazione è inaffidabile e l'hardware è a rischio rottura.

Il prossimo passo: Implementazione obbligatoria di isolatori digitali e revisione del routing PCB per separare i piani di massa logica da quella di potenza.

Sentinel Node V3.5

Il Notaio Digitale che rende obsoleta la SD-Card

Zero latenza, scritture infinite. Il dato è blindato anche se salta la corrente.

Ripristino fisico esterno. Se il firmware si pianta, il sistema reagisce.

Time-stamping deterministico. Indipendente dai server NTP esterni.

Diodi P6KE15A e Schottky. Sopravvive ai picchi industriali (14.89V testati).

Conclusioni e Sviluppi Futuri: Verso una Sentinel Inarrestabile

I dati raccolti non lasciano spazio a interpretazioni: il "funzionamento base" è il nemico giurato dell'affidabilità industriale. La nostra centralina Sentinel deve evolvere per gestire ambienti dove il rumore elettromagnetico non è l'eccezione, ma la costante. Non ci accontentiamo di un sistema che sopravvive; vogliamo un sistema che ignori il disturbo.

La sfida che ci attende riguarda l'irrobustimento strutturale della logica di controllo. Non si tratta solo di aggiungere componenti, ma di ripensare il modo in cui i segnali attraversano la board. La nostra strategia per le prossime revisioni si focalizza su:

- Ottimizzazione del Layout PCB: Analisi avanzata delle correnti di ritorno e segregazione netta tra i piani di massa della logica e quelli di potenza per abbattere il Ground Bounce alla radice.

- Filtraggio Multilivello: Integrazione di array di diodi TVS a bassissima capacità e filtri EMI di modo comune su tutte le linee di comunicazione.

- Isolamento Mirato: Implementazione di isolatori digitali ad alta velocità solo dove strettamente necessario per garantire l'integrità del bit senza saturare il bus.

L'Equazione dei Costi: La vera ingegneria non consiste nell'usare componenti "military-grade" dal costo esorbitante. La nostra filosofia è ottimizzare il BOM (Bill of Materials) attraverso un design intelligente. Spendere tempo in fase di sbroglio e simulazione permette di risparmiare sui componenti passivi, mantenendo il prezzo finale del dispositivo competitivo senza sacrificare un singolo decibel di protezione.

La Sentinel continuerà a subire test distruttivi in scenari sempre più ostili. Ogni errore catturato oggi in laboratorio è un fermo macchina risparmiato ai nostri utenti domani. La strada verso la resilienza totale è lunga, ma non abbiamo intenzione di fermarci.